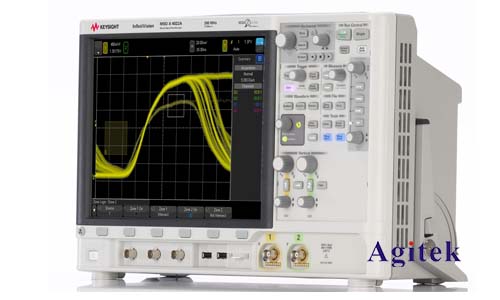

是德DSOX4024A示波器FPGA 調試解決方案

在現代電子系統設計中,FPGA(Field-Programmable Gate Array)扮演著越來越重要的角色。其強大的并行處理能力和靈活的配置特性使其廣泛應用于高速數字信號處理、通信系統以及嵌入式系統等領域。然而,FPGA設計的復雜性也帶來了巨大的調試挑戰。高效的調試策略對于縮短開發周期、降低成本至關重要。本文將重點介紹如何利用是德DSOX4024A示波器及其配套工具,構建一套完善的FPGA調試解決方案。

DSOX4024A作為一款高性能示波器,擁有豐富的功能,使其成為FPGA調試的理想選擇。其高采樣率和高帶寬能夠捕捉到FPGA內部高速信號的細微變化,從而幫助工程師快速定位信號完整性問題,例如毛刺、抖動以及過沖等。此外,DSOX4024A還支持多種協議分析,可以方便地對FPGA與其他器件之間的通信進行解碼和分析,例如I2C、SPI、UART等,這對于復雜系統調試尤其重要。

然而,僅僅依靠示波器的波形觀察往往不足以全面診斷FPGA內部的邏輯問題。為了更深入地理解FPGA的運行狀態,我們需要結合邏輯分析儀的功能。DSOX4024A可以通過選配相應的探頭和軟件模塊,實現邏輯分析功能。這使得工程師能夠同時觀察到FPGA內部關鍵信號的時序和邏輯狀態,從而更精準地定位問題根源。

在實際調試過程中,以下幾種策略能夠顯著提高效率:

1.預先規劃和充分的測試計劃:在開始FPGA設計之前,制定詳細的測試計劃至關重要。這包括定義需要測試的信號、測試點的選擇以及測試用例的設計。合理的測試計劃能夠避免調試過程中的盲目性,提高調試效率。

2.采用模塊化設計:將FPGA設計劃分成多個獨立的模塊,有助于隔離和定位故障。通過逐個模塊進行測試,可以有效地縮小故障范圍,簡化調試過程。

3.充分利用仿真工具:在FPGA設計初期,使用仿真工具進行功能驗證和時序分析能夠有效地減少潛在的問題,避免在硬件調試階段遇到難以解決的難題。

4.靈活運用DSOX4024A的各種功能:DSOX4024A提供了豐富的觸發功能、測量功能和數學運算功能,工程師需要充分利用這些功能來有效地分析信號,例如使用邊緣觸發來捕捉特定事件,使用測量功能來精確測量信號參數,使用數學運算功能來對信號進行處理和分析。

5.結合軟件調試工具:除了硬件調試工具外,利用FPGA廠商提供的軟件調試工具,例如ModelSim或Vivado等,能夠對FPGA代碼進行仿真和調試。結合硬件和軟件調試手段,可以更全面地了解FPGA的運行狀態,從而更有效地解決問題。

6.熟練掌握信號完整性分析技術:高速數字信號的完整性對FPGA的正常工作至關重要。DSOX4024A的強大分析功能,例如眼圖分析、抖動分析等,能夠幫助工程師有效地評估信號完整性,從而解決信號完整性相關的問題。

7.構建完整的調試環境:為了方便調試,建議構建一個完整的調試環境,包括電源、探頭、連接線以及必要的軟件工具。一個良好的調試環境能夠顯著提高調試效率,減少人為錯誤。

8.積累經驗,不斷學習:FPGA調試是一個需要不斷學習和積累經驗的過程。通過不斷地實踐和總結,工程師能夠更好地掌握調試技巧,提高調試效率。

總之,利用是德DSOX4024A示波器及其配套工具,結合合理的調試策略和**實踐,工程師可以構建一套高效、精準的FPGA調試解決方案,顯著縮短開發周期,提高產品質量,最終提升競爭力,如果您有更多疑問或需求可以關注安泰測試哦!非常榮幸為您排憂解難。

技術支持

關注官方微信

關注官方微信